Academic Year 2020-21

I. Departmental Events:-

- Webinar on “GATE Awareness” delivered by Imperial Institute of Excellence,Pune on March 04, 2021.

- Guest Lecture on “Aptitude Skill Development & Techniques to Crack Competitive" Exams” for Second, Third & Final Year students delivered by Career Launcher, Pune on March 03,2021.

- Online “Android development workshop” for Second, Third & Final Year students on February 27, 2021.

- Guest Lecture on “Career opportunity after B.Tech” for Second, Third & Final Year students delivered by, ACE Engineering Academy , Pune on February 26, 2021.

- Online “Students Orientation DSE -YR 2020” for DSA students on February 01 , 2021.

- Online “Parents Meeting” for Second, Third & Final Year students & their parents on January 22, 2021.

- Online “National Youth Day Celebration” on January 12, 2021.

- Online “Parents Meet” for Second, Third & Final Year students & their parents on October 28,2020.

- Online “Teachers day Celebration” on September 5,2020 .

- Online “Induction Programme”, for Second, Third & Final year on July 21,2020

- Online Workshop on “Introduction to Combinatorics” for Second ,Third & Final year students on July 18,2020 conducted by Mr.Renjith.C.V. ,Philips, Pune

Academic Year 2019-20

I. Departmental Events:-

- Online quiz on “Analog and Digital Communication” was organized for faculty and students from 28th May to 29th May 2020, during lockdown due to Covid-19.

- An online Quiz on "World Telecommunication Day” was organized for students from 17thMay to 18thMay 2020.

- An Online “Global Conference on Next Generation Information Communication Technologies-2020(GC-NGICT-2020)", organized for BE & ME students, on 10th Apr, 2020.

- Three days Aspire Skill India Training on “Field Technician-AC”, for Second year E&TC Engineering students, on 12th March,2020.

- “Prayas Camp” for students at Devgaon, Taluka-Akole, District-Ahmednagar, on 11th to 13th Feb, 2020.

- Activity during Swachhata Pakhwada "Poster Competition On Water Conservation” for second year E&TC students, on 4th Feb 2020.

- One day Workshop on “Career Guidance” to GRWP, Tasgaon Students on 25th Jan 2020,at NBNSSOE,Pune

- “Internal Hackathon 2020”, for all students, on 17th Jan, 2020.

- Workshop on “IPR (Intellectual Property Rights) " for all faculty members under STES dtd on 11th Oct.2019 from 9.00 am to 2.00 pm. by Adv.Swapnil Gawande, BLI Consultants Pvt.Ltd.

- "Japanese Audit Course- Module 1 & 2”, for Second and Third year E&TC engineering students dtd on 1st Oct 2019 from 11:00 to 1:00 pm.by, Mr.Kulkarni.

- Workshop on “Basics of Python " for Second and Third year E&TC engineering students dtd on 27th July.2019 from 9.00 am to 2.00 pm. by VIT Students.

- Workshop on “ IoT / Arduino " for Third and Final year E&TC engineering students dtd on 13th July.2019 from 9.00 am to 2.00 pm. by Mr.Navjyot Sukhmani.

- Workshop on “ Interview skills" for Final year E&TC engineering students dtd on 3rd July.2019 from 9.00 am to 2.00 pm. by Ms. Renu Kasina, Priority HR Services, Pune.

- Mini project competition for Third year E&TC engineering students dtd on 17 Sep.2019 from 9.00 am to 2.00 pm. by, Ana Digi, Pune.

- M.E. project competition for Final year E&TC Master of engineering students dtd on 27 July.2019 from 9.00 am to 2.00 pm. by, Ana Digi, Pune.

II. Events organized under Techtonic 2K20. :

“DIGI-LOGIC” Competition dated on 7th Feb 2020:

The “DIGI-LOGIC” Competition was judge by Mr. Akshay Shitole, AnaDigi. There were 47 participants. The technical test started for 47 students and there were 4 participants short listed for next round. Next round was Hands-on session on digital circuit. At the end, winner and runner was announced based on the assessment results.

“Treasure Hunt” Competition dated on 7th Feb 2020:

The “Treasure Hunt" competition was inaugurated by Chris Samuel, (HR, Cognizant)& followed by student interaction with Training & Placement Officer Mr. Abhishek Pandey at that time Principal/Director Dr. S. D. Markande, Head of Department Dr.M. M. Jadhav were also present on the Dias. It was a competition in which students participated and enjoyed a lot. And finally winner & runner was announced.

“Laser Shoot” Competition dated on 6th& 7th Feb 2020:

The “Laser Shoot" event was inaugurated by our BE student Mr.Jayant Yadav & Competition was judge by, Mr. Suraj Gaykwad, Managing Director, Solarzo Energy Solutions.Pvt.Ltd. “Laser shoot" competition is a blend of Innovative idea and Challenge with a pinch of enjoyment. It was a competition in which students & faculty participated and enjoyed a lot. And finally winner & runner was announced.

Workshop on “PCB Design “dated on 6th Feb 2020:

The “PCB Design workshop “was inaugurated by event coordinator Prof.S.Y.Tamboli and conducted by Mr.Sharvesh chopade & Shubham Badgujar, final year students of E&TC department, Sinhgad college of Engineering, Pune. In this workshop the basics of PCB Design was discussed and a hands-on session was undertaken.

“Chess-Carrom” under Chill Zone (Mini Game) dated on 6th& 7th Feb 2020:

The event “Chess-Carrom '' organized under Chill-Zone of Techtonic 2K20 in NBNSSOE PARKING AREA on 6th & 7th Feb 2020.It was a mini game in which many students & faculty participated and enjoyed a lot.

"PUBG" event under Chill zone dated on 7th Feb 2020:

The "PUBG" event was organized under Chill-Zone of Techtonic 2K20 on 7th Feb 2020 .There were total of 30 participants present for the event and enjoyed a lot.

Academic Year 2018-19

|

Sr. No

|

Name of the event

|

Date

|

No. of students participated

|

|

1

|

PCB Workshop

|

30 - 31 Aug 2018

|

46

|

|

2

|

Machine Learning

|

23, 24 & 27 Aug 2018

|

75

|

|

3

|

DIGI-LOGIC

|

20th Feb 2019

|

47

|

|

4

|

Chill Zone

|

20th Feb 2019

|

60

|

|

5

|

ELECTROBUZZ

|

21st Feb 2019

|

40

|

|

6

|

ROBO-RACE

|

22th Feb 2019

|

22

|

|

7

|

Seminar on Industrial Applications on PLC and SCADA

|

20th Feb 2019

|

45

|

|

8

|

POSTER PRESENTATION

|

23th Feb 2019

|

31

|

|

9

|

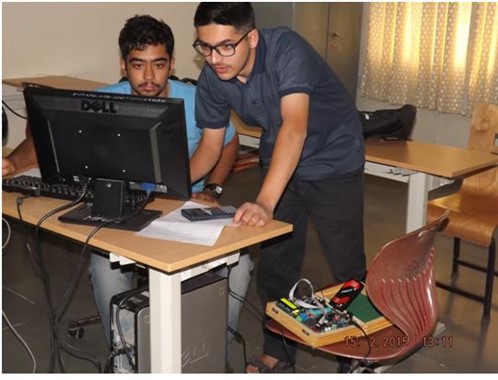

IoT Workshop

|

21st Feb 2019

|

20

|

Academic Year : 2017-18

Workshop on "Internate of Things"

- Title of the Event : Workshop on “Internet of Things

- Date of Conduction : 10 th July 2017 to 12 th July 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description : Under the part of VAP-V (Value Addition Program), workshop has been arranged. The workshop was for final year students . The resource persons were Mr. Anurag Bhanbewaal from GeeksLAB Technologies Pvt. Ltd., and Mr Rameel Mohd. from GeeksLAB Technologies Pvt. Ltd.

- Faculty Co-ordinators : Prof. H. N. Lokhande

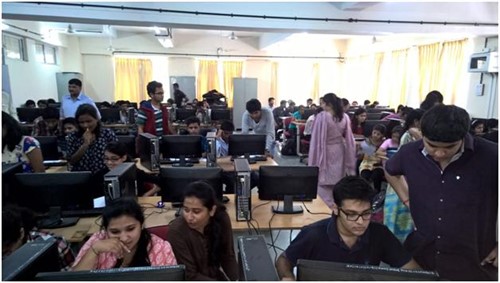

TI - MSP430” Online Quiz Competition

- Title of the Event : “TI - MSP430” Online Quiz Competition

- Date of Conduction : 29th June 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description : The “TI - MSP430” Online Quiz Competition” –under TI India University Program from Digital shark organized by E&TC Department . Winners are awarded with TI Certificates & First winner got prize of TI Innovation MSP430 Microcontroller Kit.

- Winners :Ganesh BalasahebKhandve ,Tejaswi Shamrao Patil, Durga Sandeep Tatke (BE E&Tc) , Shah Rajat Nitin, Rohit Kamble (TE E&TC)

PARENT’S MEET

- Title of the Event : Parent’s Meet

- Date of Conduction : 1st July 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description : Parent’s Meet was organized for SE, TE and BE students parents by Department of E&TC, NBNSSOE, Pune.

- Faculty Co-ordinator : Prof. D. S. Gaikwad

Academic Year 2016-17

“Project Idea Competition 2017”

- Title of the Event : “Project Idea Competition 2017”

- Date of Conduction: 24th March 2017

- Organized By: SSC – E&TC Club

- Description: The Project Idea Competition was organized with the objective to provide platform for students to showcase their ideas. Theme for the competition was ‘Technology for Humanity’. Students were encouraged to present their ideas to solve problems related to physically disabled people, healthcare, disaster management, agriculture, Smart city, Digital India etc. Mr. Mahesh Sheth Director, Tech-City Research & amp; Consulting Pvt Ltd, Pune was the judge for this competition.

- First Winner Team : Ganesh Sirvi, Nikhil Kurkure and Sumit Rathi

- Second Winner Team: Chitali Baje, Varsha Vaithla, Pratiksha Joshi and Amruta Kumbhkarna

- Faculty Co-ordinator : Prof. Prof. D. H. Gawali

Workshop on “Automation with Arduino”- Techtonic 2017

- Title of the Event : Workshop on “Automation with Arduino”-Techtonic 2017

- Date of Conduction: 12th February 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description: The Electronics & Telecommunication Engineering Department organized workshop on “Automation with Arduino” .This workshop covered Introduction to Arduino and home automation using Arduino. 61 students were participated.

- Faculty Co-ordinator : Prof. N.S.Gujar

- Student Co-ordinator: Mr. Akash Dwivedi

- Student Co-ordinator: Mr. Rishabh Bhapkar

“Techno-Quiz” Competition - Techtonic 2017

- Title of the Event : “Techno-Quiz” Competition - Techtonic 2017

- Date of Conduction: 10th February 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description: The Electronics & Telecommunication Engineering Department organized “Techno-Quiz” Competition .Competition was based on C& C++ programming.

- Winner Team : Aparna Razdan and Duhita Pradan

- Runner-up Team: Khishor Malpathak and Avanti Wadhonkar

- Faculty Co-ordinator : Prof. S. A. Sahane

- Student Co-ordinator: Mr. Rishabh Bhapkar

“DIGI LOGIC Design ” Competition - Techtonic 2017

- Title of the Event : “DIGI LOGIC Design ” Competition - Techtonic 2017

- Date of Conduction: 9th February 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Description: The Electronics & Telecommunication Engineering Department organized “DIGI LOGIC Design” Competition. The competition received an overwhelming response, 80 participants were participated.

- Winner Team : Duhita Pradhan and Ruchita Hambire

- Runner-up Team: Harshada Shirshat and Pooja Sonawane

- Faculty Co-ordinator : Prof.K.B.Kharat

- Student Co-ordinator: Mr. Shashank Upreti

“MAKING WITH PIC” Competition - Techtonic 2017

- Title of the Event : “MAKING WITH PIC” Competition - Techtonic 2017

- Date of Conduction: 10th February 2017

- Organized By : Electronics & Telecommunication Engineering Department

- Description: The Electronics & Telecommunication Engineering Department organized “MAKING WITH PIC” Competition .It has got very good response, total 80 participants were participated.

- Winner Team : Ajay zaware and Abhishek kalokhe

- Runner-up Team: Dinesh Dafale and Arshad shaikh

- Faculty Co-ordinator : Prof. H.N.Lokhande

- Student Co-ordinator: Mr. Saurabh Kulkarni

PARENT’S MEET

- Title of the Event : Parent’s Meet

- Date of Conduction : 7th Jan 2017

- Organized By: Electronics & Telecommunication Engineering Department

- Faculty Co-ordinator : Prof. Sneha Kulkarni

- Description : Parent’s Meet was organized for parents of SE, TE and BE(E&TC) students by Department of E&TC, NBNSSOE, Pune.

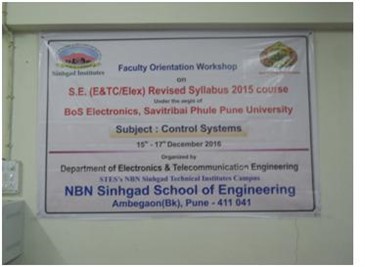

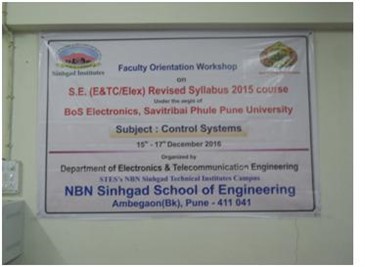

Faculty Orientation Workshop on “Control Systems”

- Date of Conduction : 15th to 17th December 2016

- Organized By: Electronics & Telecommunication Engineering Department

- Description : The Electronics & Telecommunication Engineering Department organized 3 days Faculty Orientation Workshop on SE (E&TC/Elex) Revised Syllabus 2015 Course Under the aegis of Board of Studies, Electronics, Savitribai Phule Pune University for the subject “Control Systems”. Workshop has got very good response, seventy six faculties participated from various colleges. This workshop covered all six units of the subject ‘Control Systems’.

- Faculty Co-ordinators : Prof. S. D. Sawant , Prof. J. A. Desai

Workshop on Android Application Development

- Date of Conduction : 19 th Sept 2016 to 20 st Sept 2016

- Organized By: Electronics & Telecommunication Engineering Department

- Description : Under the part of VAP-V (Value Addition Program), workshop has been arranged. The workshop was conducted on “Android Application Development”. The final year (B.E.) students were engaged with good practice with hands on experiments on Android OS & Application development. Under this workshop, students succeed in attaining exposure to latest technology available in the market and best industrial practices. This exposure helps students in understanding subject in better way and helps in great excellent while in electronic industry.

- Faculty Co-ordinators : Prof. H. N. Lokhande

Academic Year : 2015-16

Texas Instruments India Analog Maker Competition 2015

- Date of Conduction : 12 th & 22nd September 2015

- Organized By: SSC –E&Tc club

- Description : Electronic circuit design competition was conducted for UG and PG students in association with EdGate Technologies Pvt. Ltd.Under Texas Instruments India University There were two rounds . 115 groups were participated .32 groups were qualified for Round II. Two winning teams were selected from Round II.

- Winning teams - 1.Amol Datar and Akshay Waghmare - TE (E&TC)

2.Prasiddhi Khairnar and Akanksha Agarwal- ME(E&TC)

- Faculty Co-ordinator : Dr.Mrs.S. D. Shelke.

Round 1 : Design using WEBENCH

Prize Distribution: Amol Datar & Akshay Waghmare

PIC Programming Competition

- Date of Conduction : 15th February 2016.

- Organized By: SSC –E&Tc club

- Description : PIC programming Completion was conduced for E&Tc students in association with Logic Power, Pune, Sole Licensed Tool Manufacturer for Microchip in India (Prizes sponsored by Logic Power). It was conducted in three rounds.21 groups were participated.

- Winning teams: 1. Saurabh Kulkarni, Nikhil Kumar 2. Shubham Bonde, Ajay Zaware

- Faculty Co-ordinators : Dr.Mrs.S. D. Shelke , Prof. Mrs. N.S.Gujar, Prof.H.N. Lokhande.

Hardware implementation

Prize Distribution by Mr. Prashant Shirpurkar Director, Logic Power

Two days workshop on ‘CMOS IC Design using Empyrean EDA Tools’

- Date of Conduction : 29th & 30th June 2015

- Organized By: E&TC Department.

- Description : Two days workshop on ‘CMOS IC Design using Empyrean EDA Tools was conducted for faculties from different colleges under SSPU and UG/PG students. In association with Ambition Technologies and Silicon Automation Systems .

- Resource Person: Mr. Rahul Sharma, Ambition Technologies, New Delhi & Mr. Shridhar Dudam, PICT, Pune.

Mind Spark

A general knowledge quiz was conducted for UG students under the inaugural function of ‘Electronics and Telecommunication Engineering Students Association’ (ETSA).

- Faculty Co-ordinator: Mrs. S. M. Jog

- Date: 8 July 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 50

Enabling Revolution

One day seminar ‘Enabling Revolution’ for the awareness of various modern electronic equipments understanding for hands on experiences in the lab was organized under ETSA.

- Faculty Co-ordinator: Mr. P. W. Kulkarni

- Date: 20 July 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 80 (UG)

- Resource person: Atul Kuchekar (Cyronics)

VHDL Codes and Simulation

A seminar on ‘VHDL Codes and Simulation’ was organized for SE students to understand the behavioral and structural modeling in Xilinx software.

- Faculty Co-ordinator: Mrs. S. A. Sahane

- Date: 7 Sep 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 70 (UG)

- Resource person: Nagesh Vaidya (C-DAC)

Embedded Systems

A seminar on ‘Embedded Systems’ was organized for UG and PG students to create awareness about the preparation of final year projects. Few models based on embedded systems were demonstrated.

- Faculty Co-ordinator: Mrs. S. N. Kulkarni

- Date: 6 Jan 2014

- Venue: Seminar Hall (Third Floor)

- No. of participants: 70 (UG and PG

- Resource person: Aniket Katyayan, Praneet Parthi (Talent Sprint)

To Know Yourself

ETSA organized a workshop on ‘TO KNOW YOURSELF’. The guest lecturer was Dr.Aruna Kaulgud. She taught S.E & T.E students to know about you. She also explained how to speak in different area or different places for different target groups. Various management games were conducted for the students.

- Faculty Co-ordinator: Mrs. J. A. Desai

- Date: 5 August 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 70 (UG)

- Resource person: Dr. Aruna Kaulgud (Director, Rambhau Mhalgi Pratishtan)

Pipelined VLSI Architecture

‘Pipelined VLSI Architecture’ was a one day Seminar. The seminar was conducted by Dr. Mrs. Shaila Subbaraman (Doctorate from IIT, Bombay). She has covered many aspects of Pipelined VLSI Architecture. She started the session with review of high speed Architecture and introduced pipelining. Madam covered pipelined processor, parallel processing, folding, unfolding in detail. Next, she explained about pipelined algorithm, in which Feed forward cutset algorithm and coarse grained VS fine grained pipelining was discussed. Then she talked about very important topics regarding pipelining such as Power Reduction and Speed.

- Faculty Co-ordinator: Mrs. N. S. Gujar

- Date: 5 Feb 2014

- Venue: Seminar Hall (Third Floor)

- No. of participants: 56 (UG and PG)

- Resource person: Dr. S. S. Subbaraman

Scilab

Scilab is an Open source, cross platform numerical computational package and a high-level, numerically oriented programming language. It was a two- day workshop which was conducted by faculty from IIT Bombay.

- Faculty Co-ordinator: Mrs. S. S. Kukade

- Date: 5-6 Feb 2014

- Venue: Seminar Hall (Third Floor), OS and SL-II Lab (5th Floor)

- No. of participants: 63 (UG and PG

- Resource person: Mr. Swapnil More, Mr. Rupak Rokade (IIT-B)

Programmable System on Chip

A one day seminar ‘Programmable System on Chip’ was organized under Techtonic 2014. The session includes the architectures of PSOC1, PSOC2 and PSOC 3 systems as well as its applications.

- Faculty Co-ordinator: Dr. Mrs. S. D. Shelke

- Date: 6 Feb 2014

- Venue: Seminar Hall (Third Floor)

- No. of participants: 83 (UG and PG)

- Resource Person: Mr. S. S. Dudam

Seminar on Arm

The resource person covered ARM architecture including features, various modes, registers in each modes and on-chip peripherals. He also explained the programming model for ARM system development. He introduced various industrial applications on ARM9.

- Faculty Co-ordinator: Dr. Mrs. S. D. Shelke

- Date: 7 Sep 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 20 (PG)

- Resource Person: Mr. Siddharth Gore, Marvell Semiconductors

Android

Mr. Sudhish, Talentsprint conducted two-day workshop on Android. He covered the session from exam point of view in addition to giving lots of inputs for Android-based projects. The sessions were thoroughly conducted. They were structured and had good blend of theory and hand-on sessions.

- Faculty Co-ordinator: Dr. Mrs. S. D. Shelke

- Date: 10-11 Oct 2013

- Venue: Seminar Hall (Third Floor)

- No. of participants: 20 (PG)

- Resource Person: Mr. Sudhish, Talentsprint Education Services, Hyderabad

MATLAB for Signal Processing

The resource person introduced the toolbox for Signal processing in MATLAB. He demonstrated the use of the toolbox for audio signal processing. He also showed the application of various filters on the audio signal and compared the performance of the filters. He explained how MATLAB is used for application development in industry.

- Faculty Co-ordinator: Dr. Mrs. S. D. Shelke

- Date: 14 Feb 2014

- Venue: Seminar Hall (Third Floor)

- No. of participants: 20 (PG)

- Resource Person: OTIS Elevator Company, Pune

Syllabus Revision of TE (E & TC / Electronics), 2012 Course

Honorable BOS Chairman and Principal RSCOE, Dr. D. S. Bormane and BOS member and Principal SCOE, Dr. S. D. Lokhande conducted the meeting along various experts invited from various engineering colleges in the university. 38 participants attended the workshop including BOS members, Academic Council members, Senate members, Principals, Heads of departments and senior faculty members. Dr. M. B. Mali, HOD (E & TC), SCOE and Dr. Y. Ravinder, HOD (E & TC), PICT delivered presentations on the proposed structure of TE (E & TC) subjects. Prof. D. G. Bhalke, HOD, RSCOE and Prof. D. M. Chandwadkar, HOD, K. K. Wagh IEER, Nashik delivered presentations on TE (Elex) subjects.

- Faculty Co-ordinator: Dr. Mrs. S. D. Shelke

- Date: 3 Mar 2014

- Venue: Seminar Hall (Third Floor)

- No. of participants: 38

- Resource Person: BOS Chairman and Principal RSCOE, Dr. D. S. Bormane